AMD’s recent decision to disable the loop buffer in its Zen 4 architecture might seem like a minor adjustment at first, but the broader implications invite careful scrutiny. In an era where CPU performance and security dominate tech discussions, it’s essential to delve into the subtleties and repercussions of this move for both enthusiasts and industry professionals.

Understanding Loop Buffers

A loop buffer serves as a small, high-speed cache for instructions that have been fetched but not yet executed. By storing frequently accessed instructions, loop buffers enhance performance and energy efficiency. They allow processors to mitigate redundancy in instruction execution, effectively smoothing data flow and preventing bottlenecks. Such improvements are crucial for users engaged in resource-intensive applications, where even slight optimizations can lead to noticeable differences in experience.

Insider Insights on Zen 4

The Zen 4 architecture represented a considerable leap forward for AMD, with numerous features developed for enhanced performance and efficiency. The loop buffer was a key aspect intended to optimize instruction handling. While well-received, its utility has come under scrutiny in light of recent developments, showcasing the constant evolution of AMD’s processing strategies.

Unpacking AMD’s Decision

The conversations from AMD during Hot Chips 2024 shed light on the rationale behind the removal of the loop buffer. The company indicated that the loop buffer’s primary role was as a power optimization mechanism, not a significant performance driver. Initial evaluations suggested that the differences observed with the loop buffer enabled versus disabled were minimal. This may have led AMD to reassess the necessity of this feature, prompting their decision to discontinue it.

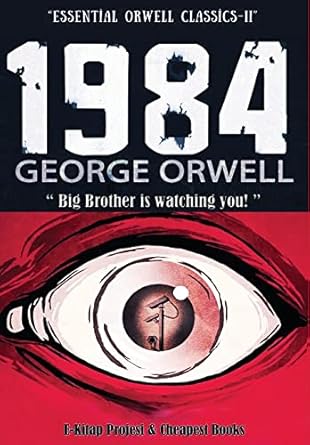

Community Voices and Concerns

Following the announcement of the loop buffer’s discontinuation, a lively discussion has emerged among the tech community. Many voices within the enthusiast space have raised concerns over the possible security implications this change might evoke. Some worry that the removal could expose subtle vulnerabilities, reflecting ongoing anxieties regarding CPU safety that have intensified in recent years. The community is eager to understand how these engineering decisions might impact their usage and potential risks, with discussions intensifying around the weighty role that CPU architecture plays in today’s technology landscape.

Looking Ahead at AMD’s Strategy

The discontinuation of the loop buffer signals a potential shift in AMD’s approach to hardware design and optimization strategies. What some may view as a setback illustrates AMD’s flexibility and commitment to learning from prior iterations. This openness to refining processes could pave the way for more robust designs in upcoming hardware releases, ultimately enriching the computing experience for users.

Final Reflections

While the disabling of the loop buffer may appear to be a small change, it opens up important discussions about AMD’s engineering decisions and their implications for the future of hardware innovation. As the CPU landscape continues to evolve, community feedback will play an essential role in shaping AMD’s trajectory. What are your thoughts on this decision? Does this mark a larger trend in CPU design? Join the conversation and share your perspectives!

“AMD never advertised or documented the feature beyond dropping a line in the Processor Programming Reference.” Source

“It’s a clear contrast to Intel, which often documents its loop buffer…”